728x90

1. 컴퓨터 = 입력장치 + 출력장치

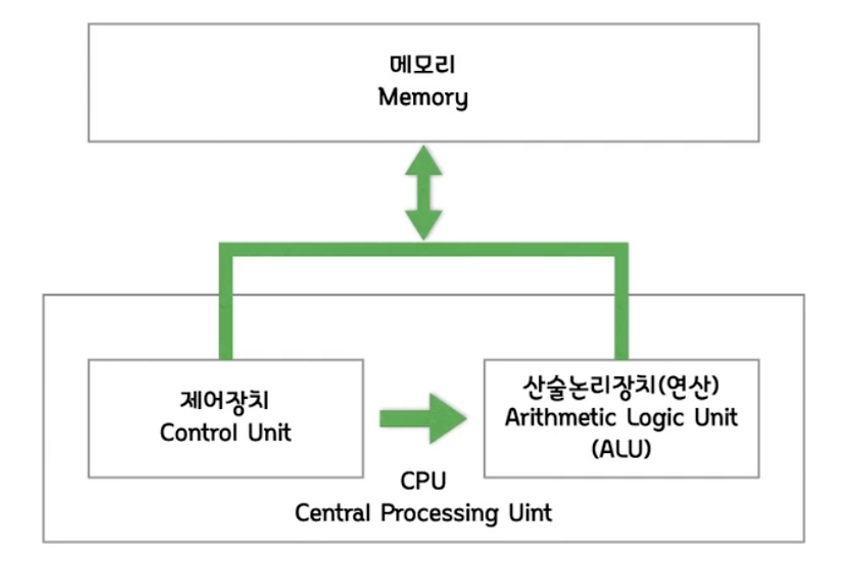

2. CPU

- CPU의 구성

- ALU : 연산장치 - 산술연산과 논리연산을 계산하는 디지털 회로

- CU : 제어장치 - 순서 제어

- 레지스터 - 처리할 명령어 저장

- 캐시 메모리(L1) - 처리 속도 증가

-

- 클럭 : CPU 내부에서 일정한 주파수를 가지는 신호

- 이 신호로 모든 명령어가 동작하게 된다.

- 1Hz(헤르츠)면 1초에 1번 1기가 헤르츠라고 하면 1초에 1기가만큼(1024메가), 즉 10억 번

- 클럭 주파수가 빠를수록 제한된 시간에 더 많은 명령을 처리 > 좋은 성능의 중앙 처리 장치

- 코어

- 중앙처리 장치 역할을 하는 블록

- 멀티 코어 : 많은 연산을 빠르게 병렬 처리

3. 메모리

- 메모리

- 레지스터 = CPU

- 캐시메모리(SRAM), 메인 메모리(DRAM) = 주 기억장치

- CPU가 사용하기 좋도록 각종 정보를 임시 저장하는 휘발성 장치입니다.

- SRAM vs DRAM

- 정적 메모리

- 전원 공급이 되는 동안은 기록된 내용이 지워지지 않기 때문에 재충전이 필요 없다.

- 접근 속도가 빠르고 가격이 비싸다

- 주로 캐시메모리나 레지스터로 사용

- DRAM - Dynamic RAM

- 동적 메모리

- 전원이 계속 공급되더라도 주기적으로 재충전되어야 기억된 내용을 유지

- 주로 대용량의 기억장치에 사용되며 가격이 저렴

- 주로 RAM이라고 표현하는 것(주기억장치)은 거의 DRAM

- SRAM - Static RAM

- 하드디스크(HDD) = 보조 기억장치

- 보조 기억장치

- 컴퓨터 전원이 꺼져도 지워지지 않는 저장공간

4. CPU와 메모리의 동작

- 주기억장치: 입력 장치에서 입력받은 데이터 or 보조기억장치에 저장된 프로그램을 읽어온다.

- CPU : 주기억장치에 저장된 프로그램 명령어와 데이터를 읽어와 처리

- CPU : 결과를 다시 주기억 장치에 저장

- 주기억장치 : 처리 결과를 보조기억장치에 저장 or 출력장치로 보내서 출력

- 제어장치(CU) : 1~4번 과정에서 명령어가 순서대로 실행되도록 각 장치들을 제어

5. CPU 와 메모리 구조

- 하버드 구조

- 장점 : 메모리가 두개이기 때문에 역할이 나누어져 있으며 속도가 빠르다.

- 단점 : 구성이 많기 때문에 비싸며, 복잡한 구성으로 고장이 날 확률이 높다

- 폰노이만 구조

- 프로그램 메모리와 데이터 메모리가 구분되어 있지 않고 하나의 버스를 갖는다.

- 이로 인해서 병목현상이 일어남

- 개선된 구조

- 하버드 구조 + 폰노이만 구조

- CPU의 캐시 메모리 형상에 관여

- CPU 내부 - 하버드 : CPU 내부에 캐시를 둬서 RAM과 CPU 간의 속도 차이를 줄이려고 노력

- CPU 외부 - 폰노이만 : 메모리 하나에 하나의 버스를 가지는 구조이기 때문에 병목현상이 아직까지는 존재한다

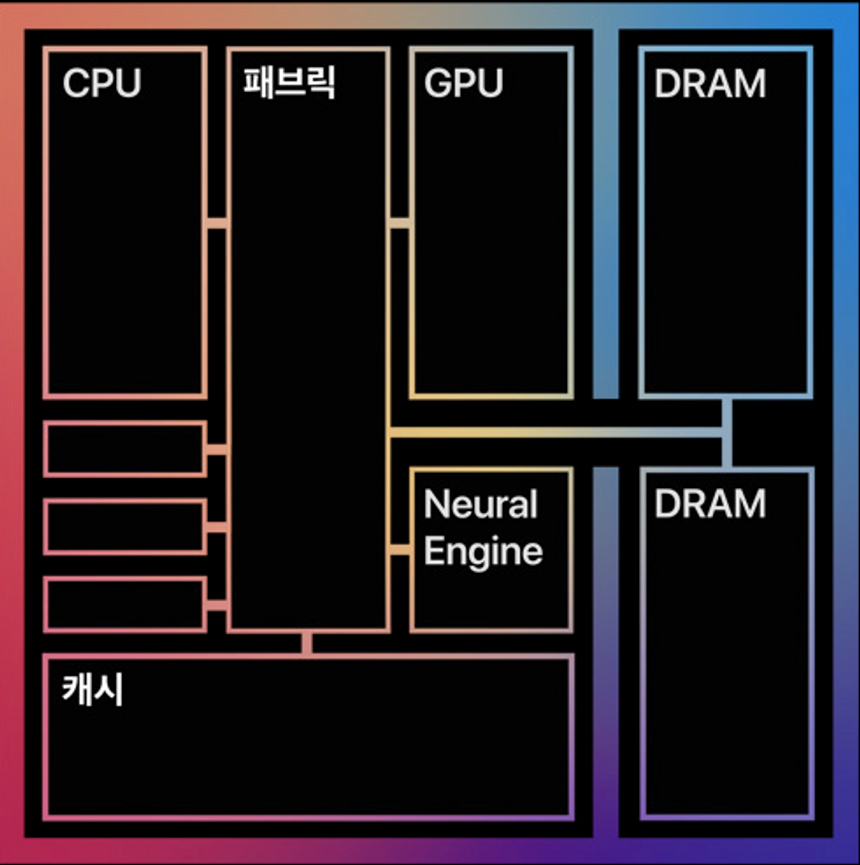

6. 맥북의 CPU 예시

- 맥북의 M1, M2 칩

- 장점 : 장치간의 거리도 짧고 통합 메모리 구조를 가졌기에 CPU의 효율을 극대화

- 단점 :

- 하나의 칩 형태로 나왔기에 RAM(주 기억장치)을 추가 한다던지의 자유도는 매우 떨어짐

- 사전에 정해진 형태로만 메모리간에 통신하기 때문에 메모리별 최적화가 적용되어있는 일부 프로그램은 동작하지 않을 수 있다. (호환성 문제)

- CPU의 동작

- 데이터를 가져오기(Fetch)

- 디코딩(Decoding)

- 실행(Execute)

'학습 내용 정리 > Computer Science' 카테고리의 다른 글

| 웹 접근성 (Web Accessibility) (2) | 2023.10.12 |

|---|---|

| 시간 복잡도 (0) | 2023.09.15 |

| 공간 복잡도 (0) | 2023.09.15 |

| 자료와 자료구조 (0) | 2023.09.11 |

| DBMS (0) | 2023.08.30 |